QUESTION IMAGE

Question

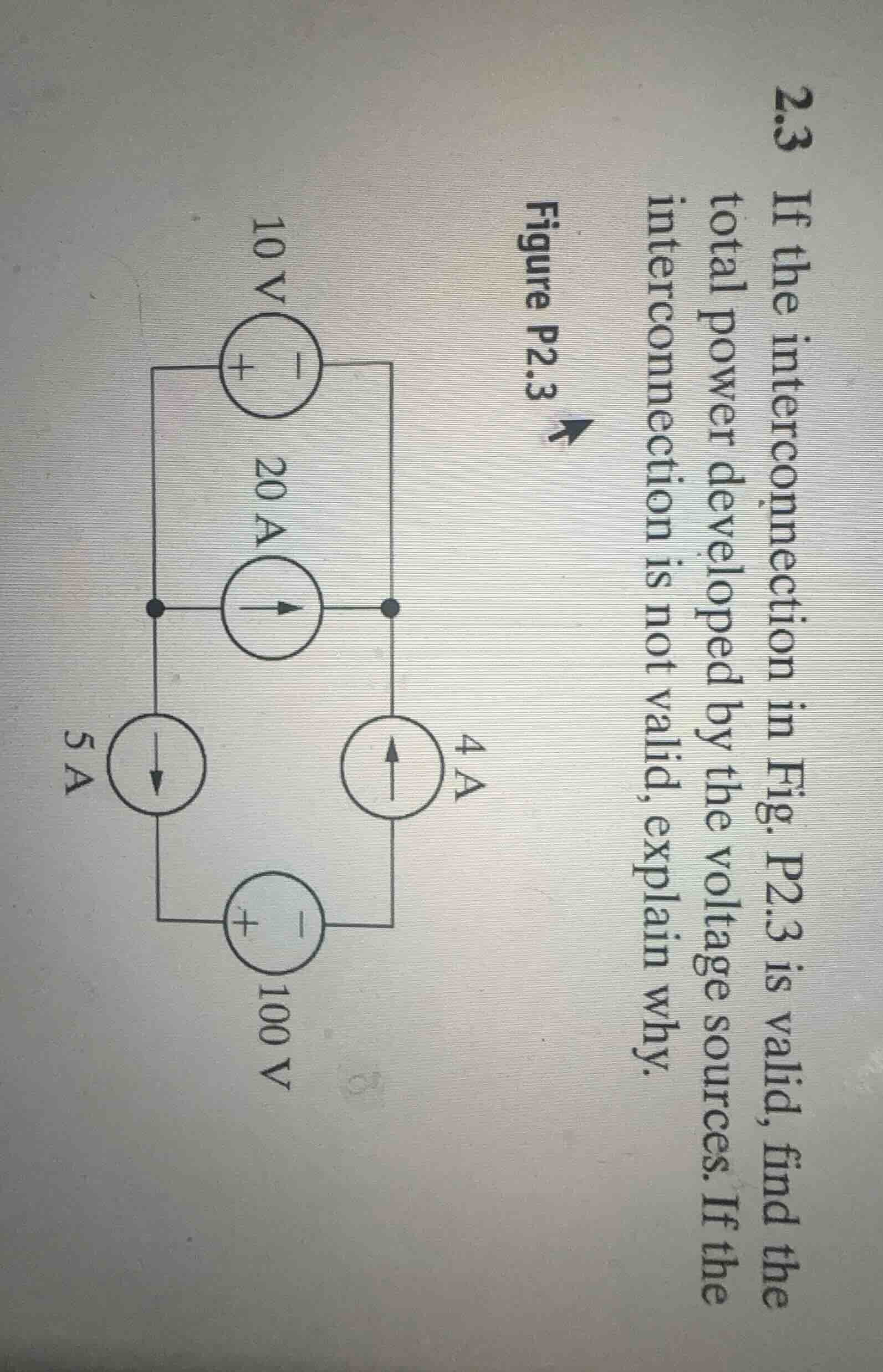

2.3 if the interconnection in fig. p2.3 is valid, find the total power developed by the voltage sources. if the interconnection is not valid, explain why. figure p2.3

Step1: Check KCL at the nodes

First, we analyze the currents at the nodes. Let's consider the top node (connected to the 10V source and the 20A, 4A, 5A currents). The sum of currents entering a node should equal the sum of currents leaving. Let's define the direction: currents going up are positive, down are negative.

For the top node: Current from 20A source (up) + 4A (up) - 5A (down) should equal the current through the 10V source. Wait, but also, we need to check the voltage sources. Wait, actually, first, check if the current sources and voltage sources are compatible. Wait, the two voltage sources: 10V and 100V. Wait, the 10V source is in parallel with a 20A current source, and the 100V source is in parallel with 5A and 4A. Wait, but for a valid interconnection, the voltage across parallel elements must be equal. Wait, the 10V source and the 20A current source are in parallel, and the 100V source is in parallel with 5A and 4A. But also, the two parallel branches (10V with 20A, and 100V with 5A and 4A) are connected? Wait, no, looking at the circuit: the top branch has 10V and 20A in parallel, the bottom branch has 100V, 5A, and 4A. Wait, but the nodes: the left node is connected between 10V's + and 5A's top, and the right node is connected between 10V's - and 4A's top. Wait, maybe I misread. Wait, the 10V source is + on left, - on right. The 20A source is pointing up (so from right node to left node? Wait, no, current source direction: 20A is pointing up, so from bottom to top? Wait, maybe better to apply KCL at the two nodes (left and right).

Left node: connected to 10V's +, 5A's top (5A is going down, so leaving left node), and 100V's +? Wait, no, the 100V source is + on left, - on right. So left node: 10V's +, 100V's +, 5A's top (5A down, so current leaving left node is 5A), and the 20A source's left terminal? Wait, the 20A source is between left and right nodes, pointing up (so current from right node to left node? No, current source direction: arrow up means current flows from bottom to top, so from right node (bottom) to left node (top)? Wait, maybe this is getting too complicated. Wait, the key issue: the two voltage sources (10V and 100V) are in parallel? Wait, no, they are in different branches. Wait, no, the 10V source is across the 20A current source, and the 100V source is across the 5A and 4A current sources. But the two branches (10V-20A and 100V-5A-4A) are connected at the left and right nodes. So the voltage across the left and right nodes should be equal for both branches. But 10V ≠ 100V, which is a problem. Wait, that's a mistake. Wait, no, maybe I misread the circuit. Wait, the 10V source is in parallel with the 20A current source, and the 100V source is in parallel with the 5A and 4A current sources, but the two parallel branches (10V-20A and 100V-5A-4A) are connected in series? No, that can't be. Wait, actually, the circuit has two nodes: left and right. The left node is connected to 10V's +, 100V's +, and 5A's top (5A is going down, so current from left node to ground? No, 5A is a current source going down, so leaving left node). The right node is connected to 10V's -, 100V's -, 4A's top (4A going up, so entering right node), and 20A's top (20A going up, entering right node). Wait, now apply KCL at left node: currents entering left node: from 10V's + (but voltage source current is unknown), from 100V's + (unknown). Currents leaving left node: 5A (down). At right node: currents entering right node: 20A (up), 4A (up). Currents leaving right node: from 10V's - (unknown), from 100V's - (unknown). But also,…

Snap & solve any problem in the app

Get step-by-step solutions on Sovi AI

Photo-based solutions with guided steps

Explore more problems and detailed explanations

The interconnection is invalid because two voltage sources with different voltages (10 V and 100 V) are connected in parallel (across the same two nodes), which violates the requirement that parallel elements must have the same voltage. This would lead to a contradiction in the voltage across the nodes, making the interconnection invalid.